## **Architecture and Design Methodology** for Autonomic System-on-Chip (ASoC)

A. Bernauer, W. Rosenstiel Wilhelm-Schickard Institute for Informatics **Computer Engineering** University of Tübingen

O. Bringmann, Forschungszentrum Informatik Karlsruhe

asoc@informatik.uni-tuebingen.de

A. Bouajila, J. Zeppenfeld, W. Stechele, A. Herkersdorf Institute for Integrated Systems Munich University of Technology

#### **Reducing Design Effort**

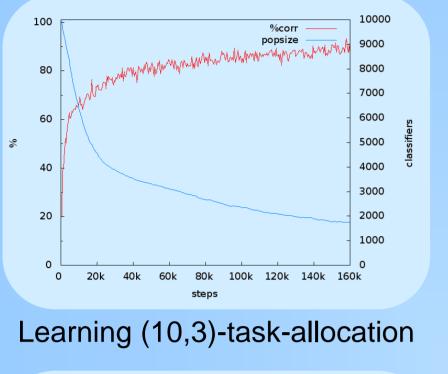

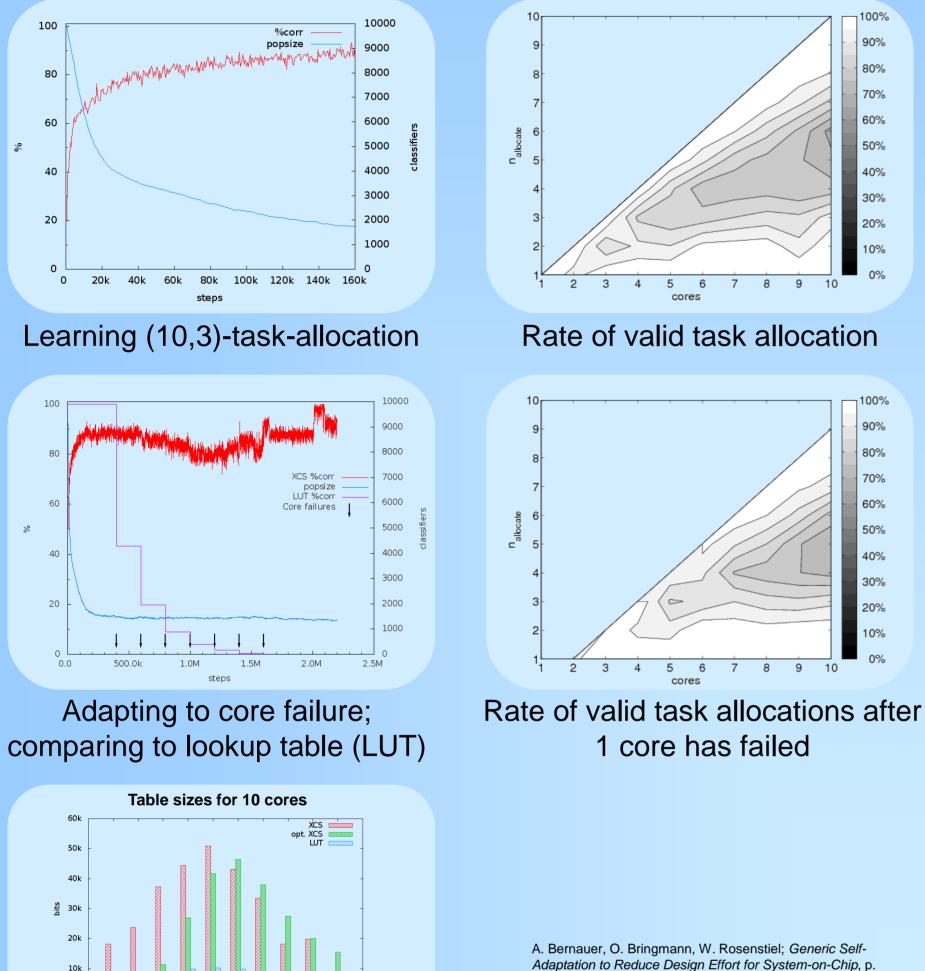

#### **XCS** helps reduce design effort

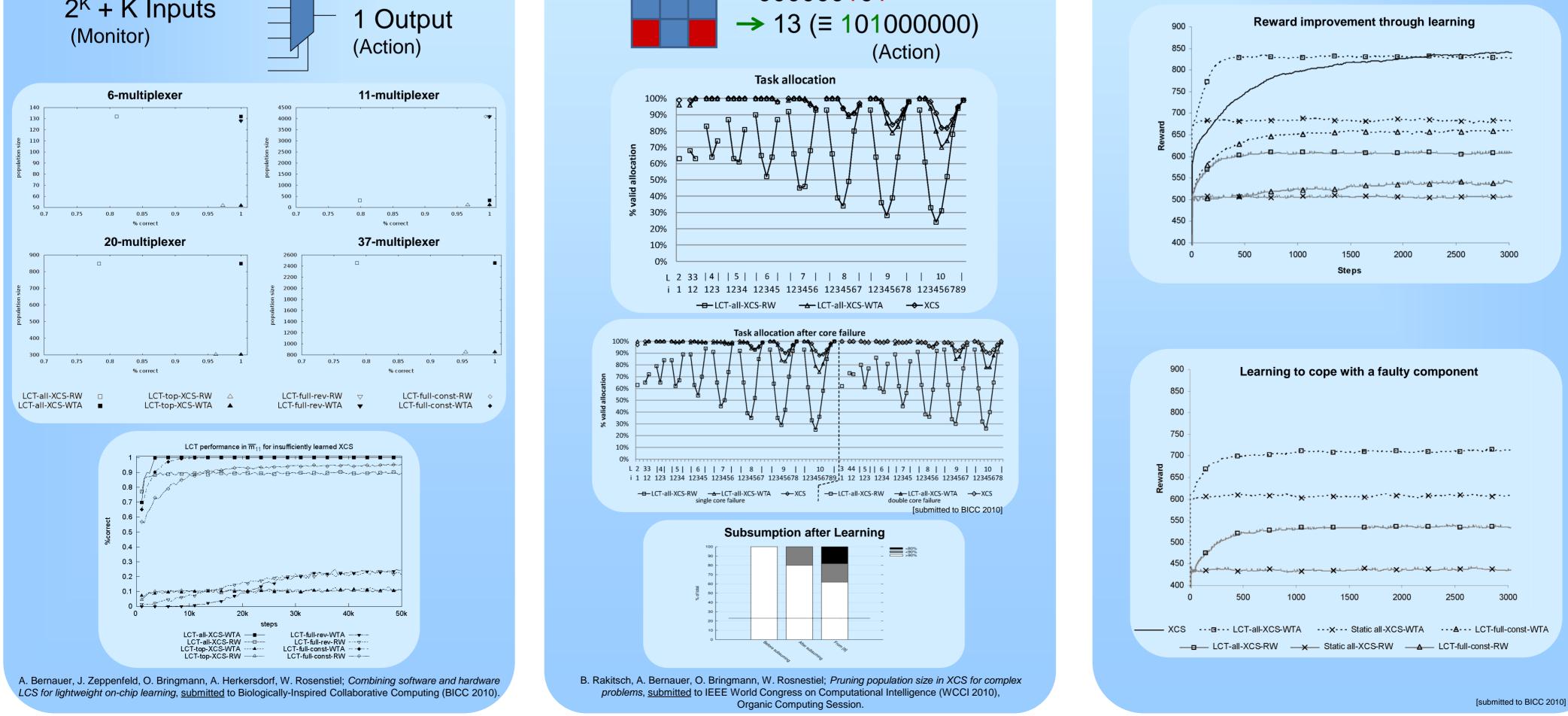

- Solves problem of task allocation

- Adapts to unexpected event of core failure

- Manageable table sizes

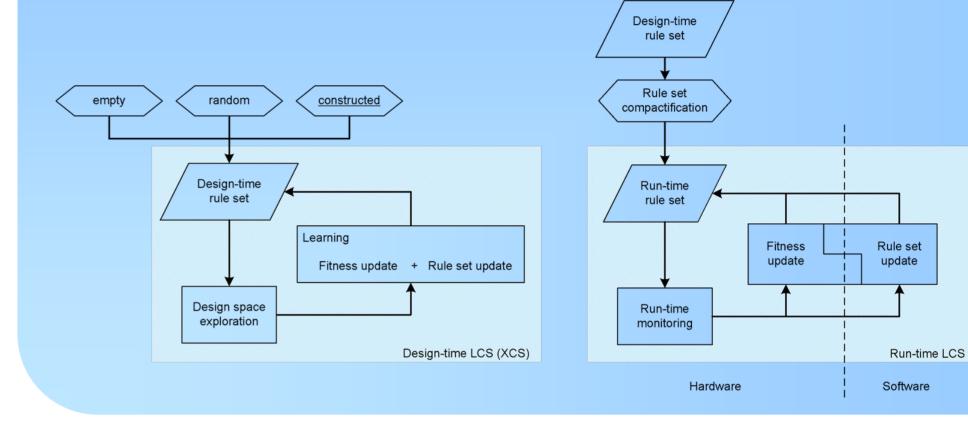

#### **Design and Run Time Learning**

### **ASoC FPGA Prototype**

SoC with autonomic capabilities on Xilinx FPGA board

- Autonomic and functional layer

- Autonomic Element Interconnect (AEI): connect different AE elements in order to provide system-wide optimizations

- Functional IPs augmented with autonomic elements (incl. LCTs)

- Functional layer: MPSoC based on multiple Leon3 processors

- LCT evaluator: 51 slices

- AEI interface: 260 slices (64 bit payload)

- Round trip latency: 4–328 cycles with 4 AE nodes

J. Zeppenfeld, A. Herkersdorf; Autonomic Workload Management for Multi-core Processor Systems, ARCS 2010.

# CPU Core

AE ring

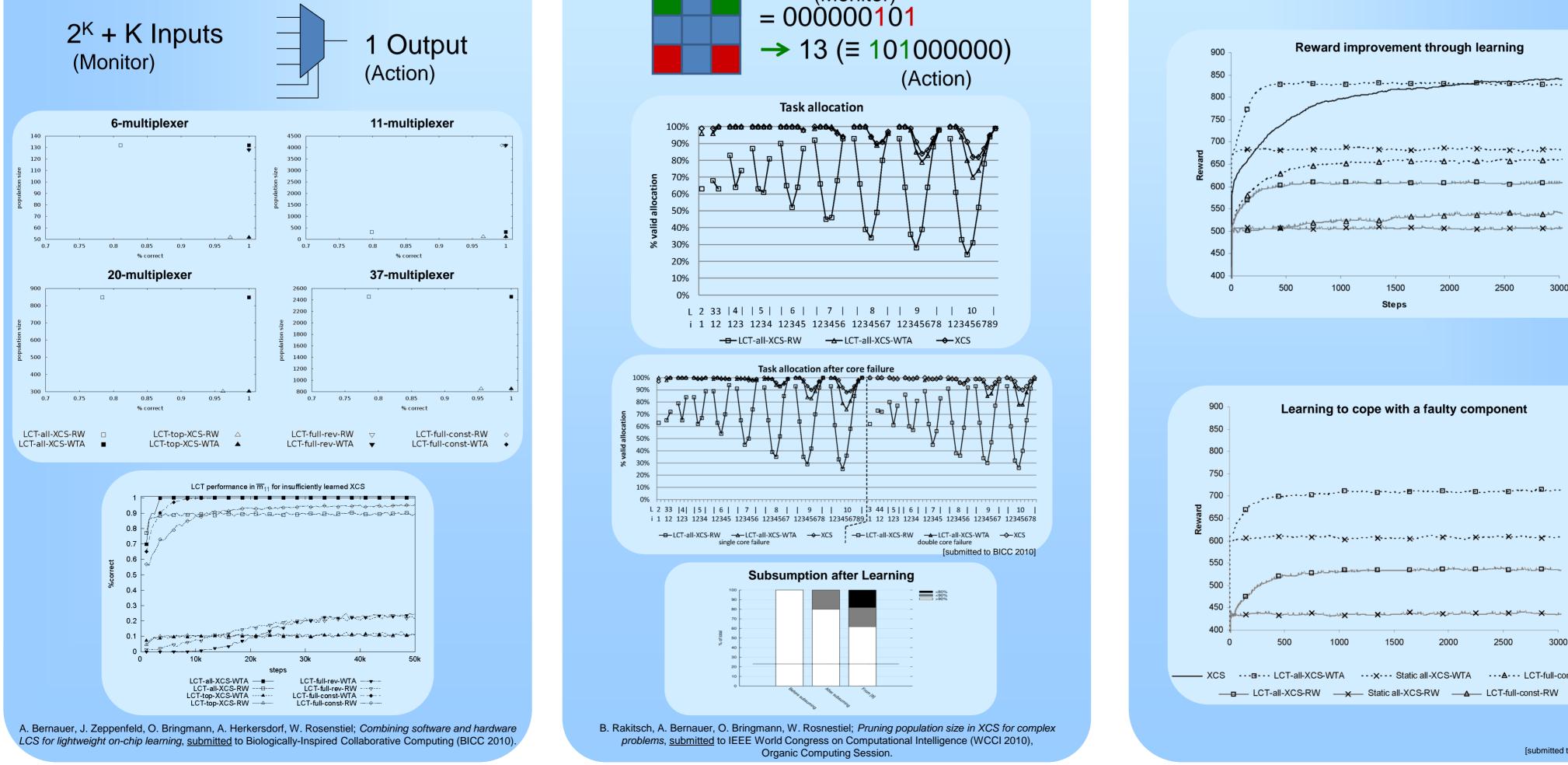

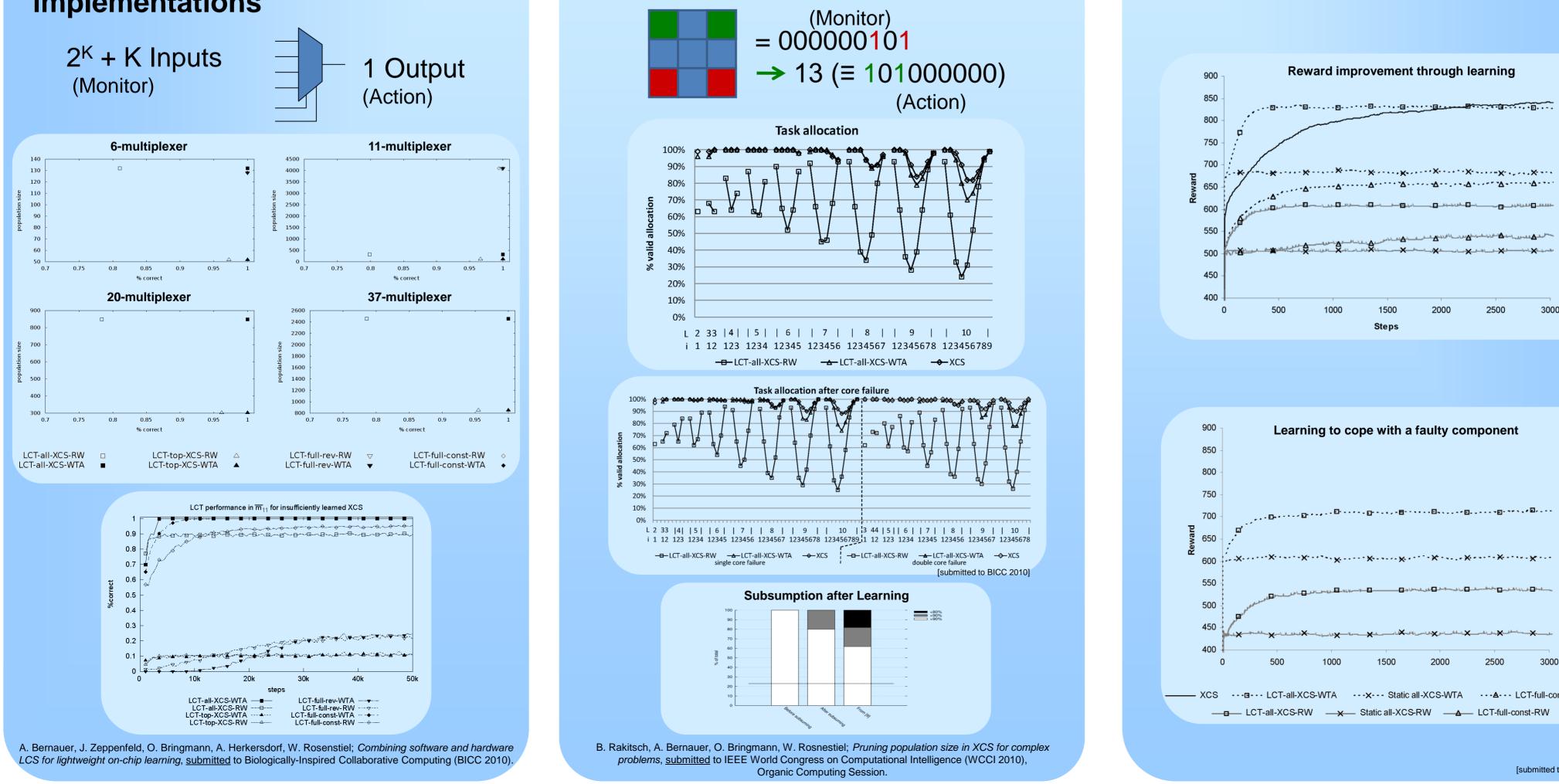

**Multiplexer Benchmark**

**Standard benchmark for** comparison with other LCS implementations

0 1

2 3

#### **Task Allocation**

Finding a valid task allocation over multiple cores

126-135, IEEE International Conference on Self-Adaptive and Self-Organizing Systems (SASO), p.126-135, San Francisco,

#### **Core Parameterization**

Adjusting frequency to maximize utilization

This work is partially funded by Deutsche Forschungsgemeinschaft (DFG) within the priority program "Organic Computing" (SPP 1183) under the grants HE 4584/3-3 and RO 1030/14-3.